### WELCOME FROM THE GENERAL CHAIR

On behalf of the entire IEDM committee, it is my absolute pleasure to welcome you to the 2023 IEDM in San Francisco from December 9-13, 2023. I am pleased to state that the conference continues its long tradition as the world's premier venue for presenting the latest breakthroughs in semiconductor technologies and devices, as shown in our promotional video at <a href="IEDM 2023 video">IEDM 2023 video</a>. As every year, IEDM 2023 will feature outstanding contributed and invited papers from industrial and academic leaders as well as students from around the world. An outline of the technical program and short summaries of all the papers are available on the IEDM website—<a href="http://www.ieee-iedm.org/">http://www.ieee-iedm.org/</a>. The electronic digest will also be available through IEEE Xplore after the conference.

The meeting kicks off on Saturday, December 9, with our popular and highly successful tutorials. Now in their 13<sup>th</sup> year, they are targeted at students, practitioners or anyone who is looking for the connection between text-book level knowledge and leading-edge current research. The topics for 2023 are: "Innovative Technology for Beyond 2 nm", "CMOS+X: Functional Augmentation of CMOS for Next-Generation Electronics", "Reliability Challenges of Emerging FET Devices", "Advanced Packaging and Heterogeneous Integration - Past, Present & Future", "Synapses, Circuits, and Architectures for Analog In-Memory Computing-Based Deep Neural Network Inference Hardware Acceleration", "Tools for Device Modeling: From SPICE to Scientific Machine Learning". On Sunday, two comprehensive short courses will be offered: "Transistor, Interconnect, and Chiplets for Next-Generation Low-Power & High-Performance Computing", and "The Future of Memory Technologies for High-Performance Memory and Computing". The short courses are organized and presented by internationally recognized researchers and technologists from industry and academia active in these areas. The topics and instructors have been carefully chosen to have broad appeal to IEDM participants and will include material suitable for both newcomers and experts.

The main conference will open with the Plenary Session on Monday morning with three featured talks. First, Siyoung Choi from Samsung Foundry Business will talk about "Redefining Innovation: A Journey forward in the New Dimension Era", followed by Thy Tran from Micron who will address "Making Memory Magic and the Economics Beyond Moore' Law", and finally Björn Ekelund from Ericsson who will talk about "Semiconductor Challenges in the 5G and 6G Technology Platforms".

In addition to the excellent contributed paper sessions, four special Focus Sessions will feature talks from leading experts in exciting new and rapidly advancing areas. The topics are 3D Stacking for Next-Generation Logic & Memory by Wafer Bonding and Related Technologies, Logic, Package and System Technologies for Future Generative AI, Neuromorphic Computing for Smart Sensors and Sustainability in Semiconductor Device Technology and Manufacturing.

On Tuesday evening, we will feature an interactive panel session on "Al: Semiconductor Catalyst? Or Disrupter?", which will bring together industry experts to have a conversation on how Al is changing the semiconductor industry and to ask them how they are using Al to transform their efforts. On Tuesday, we present the entertaining IEDM Career Luncheon at 12:20 p.m.. Isabelle Ferain from GlobalFoundries and Ilesanmi Adesida from Nazarbayev University, Kazakhstan will share their personal perspectives and their career paths in the semiconductor industries and academia, in an interactive session with a focus on students and young professionals. The discussion will be moderated by Jennifer Zhao from asm OSRAM USA Inc

IEDM 2023 will host an Exhibits section where you can look around and learn more about the latest products and publications. Stop by any time during the exhibition open hours to browse the booths and interact with the participating vendors.

I want to express my sincere appreciation to all authors and speakers who contributed to the technical program. Your efforts are the engine that continues to make IEDM the premier conference in electron devices and related technologies. I also wish to thank each of the members of the IEDM executive and technical subcommittees whose dedication and effort were critical in planning and organizing the 2023 conference.

IEDM is sponsored by the IEEE Electron Devices Society. If you are not already an IEEE and EDS member, please consider joining this great institution that has played such an important role globally for over 130 years. More detailed information regarding the IEEE is available at the conference and on their website – http://www.ieee.org.

It is my great honor and pleasure to extend a warm welcome to everyone attending the 2023 IEEE International Electron Devices Meeting from around the world.

General Chair

Dina Triyoso General Chair

Kirsten Moselund Technical Program

Jan Hoentschel Technical Program Vice Chair

Dina Triyoso

### **Executive Committee**

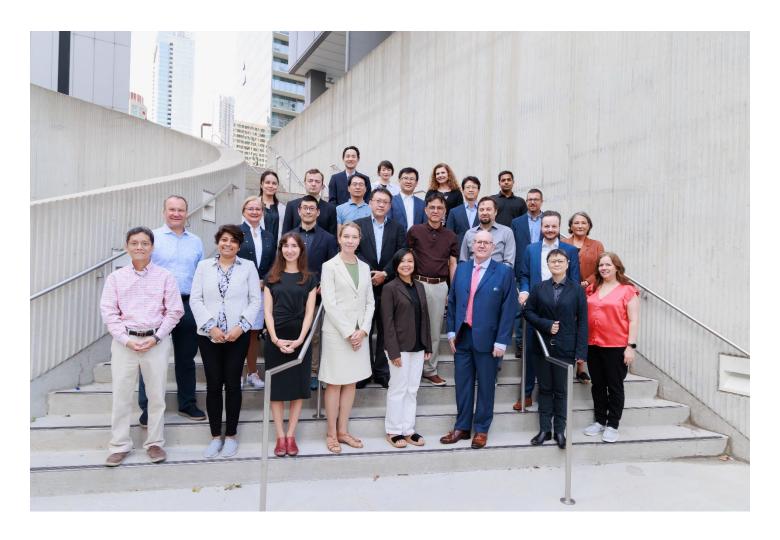

Front row left to right: Jungwoo Joh, Publicity Chair; Srabanti Chowdhury, Focus Session Co-Chair; Jean Anne Incorvia, Courses Chair (Tutorials); Kirsten Moselund, Technical Program Chair; Dina Triyoso, General Chair; Jan Hoentschel, Technical Program Vice-Chair; Sandy Liao, Asian Arrangement Chair; Shawn Boon, Conference Manager

Second row left to right: Gaudenzio Meneghesso, Courses Chair; Kirsten Weide-Zaage, European Arrangements Chair; Rihito Kuroda, Publications Co-Chair; Marvin Chang, Publications Chair; Hsiang-Lan Lum, MT Chair; Uygar Avci, Virtual Arrangements Chair; Zlatan Stanojevic, MS Chair: Phyllis Mahoney, Conference Manager

Third row left to right: Pei-Jean Liao, RSD Chair; Geert Eneman, Focus Session Chair; Chan Lim, Asian Arrangements Chair; Dechao Guo, Courses Chair (Short Courses); Kang-III Seo, Publicity Co-Chair; Lucio Pancheri, ODI Chair

Fourth row left to right: Sangbum Kim, NC Chair; Naomi Yoshida, ALT Chair; Olga Spahn Blum, PMA Chair; Arvind Balijepalli, SMB Chair

Missing: Elena Gnani, EDT Chair; Polly Hocking, Conference Manager; Gail Sparks-Riegel, Conference Manager; John Paul Strachan, European Arrangements Chair

## Intro

IEEE International Electron Devices Meeting (IEDM) is the world's preeminent forum for reporting technological breakthroughs in the areas of semiconductor and electronic device technology, design, manufacturing, physics, and modeling. IEDM is the flagship conference for nanometer-scale CMOS transistor technology, advanced memory, displays, sensors, MEMS devices, novel quantum and nano-scale devices and phenomenology, optoelectronics, devices for power and energy harvesting, high-speed devices, as well as process technology and device modeling and simulation.

## Digital & social media

LinkedIn: https://www.linkedin.com/groups/7475096/

• Twitter: <a href="https://twitter.com/ieee\_iedm">https://twitter.com/ieee\_iedm</a>

Facebook: https://www.facebook.com/IEEE.IEDM

YouTube: <a href="https://www.youtube.com/channel/UC9X-8YPHtsy3SMQwU0yZdTg">https://www.youtube.com/channel/UC9X-8YPHtsy3SMQwU0yZdTg</a>

Wikipedia: <a href="https://en.wikipedia.org/wiki/International Electron Devices Meeting">https://en.wikipedia.org/wiki/International Electron Devices Meeting</a>

## Topics of Interest ADVANCED LOGIC TECHNOLOGY (ALT)

Papers are solicited in the areas of CMOS platform technologies and applications (e.g., HPC, LOP, mobile, automotive, low-temperature CMOS, etc.), logic devices and circuits, process integration schemes for advanced nodes, innovations in material, process and metrology techniques, and design technology co-optimization (DTCO) and system technology co-optimization (STCO). Platform technologies include state-of-the-art Si and beyond-Si channel devices, gate-all-around devices, stacked devices with different polarity transistors, advanced interconnect, novel power distribution integration schemes, heterogenous 2.5D/3D integration schemes, and BEOL compatible transistors. Device architecture, device design and analysis, process integration, module advancements in process and patterning, metrology, physical layout effects, techniques for reduced variability, yield, thermal management, methodologies and solutions for DTCO/STCO in the solicited areas are of high interest.

## **EMERGING DEVICE and COMPUTE TECHNOLOGY (EDT)**

Papers are solicited on emerging nano-electronic devices and physics. This includes devices based on novel transport and control mechanisms such as tunnel FET, negative capacitance FET, cold-source FET, topological materials and devices, phase transitions, ferroelectrics and quantum effects. Devices based on low-dimensional systems including 2D materials, CNTs, nanowires, single electron transistors and quantum dots are welcomed. Exploratory devices with novel device functions and/or novel materials for neuromorphic compute, approximate and analog compute, and non-charge-based compute such as spintronics are key topics. Furthermore, emerging state machines and time dynamical compute systems are also of interest. Qubit devices as well as devices and systems designed to enable quantum computing, quantum simulation and quantum annealing are of high interest. Papers in EDT focus primarily on device physics and novel elaboration concepts.

## MEMORY TECHNOLOGY (MT)

Papers are solicited in the areas related to embedded and standalone memory technology. This includes advances in both conventional memories including SRAM, DRAM and Flash, and emerging memories including ReRAM, MRAM, PCRAM, ferroelectric memory, crosspoint memory and selectors, organic memory and NEMS-based memory, as well as their applications in the areas of Al and near-Memory compute. Topics span from demonstration of novel device concepts to fully integrated memory arrays, and from product prototyping to manufacturing related challenges and solutions. Demonstrations of manufacturing maturity of emerging memories and future scaling of conventional memories to solve the memory wall issues are of high interest. Submission of papers on novel device concepts and demonstrations, novel integration schemes, novel circuit design schemes, and novel memory architectures that enhance memory performance, scaling, 3D stacking, capacity/bandwidth increasing, and power/energy reduction are strongly encouraged. Papers based on novel device physics and in-memory computing may be transferred to EDT or NC at the discretion of the committee.

### **MODELING and SIMULATION (MS)**

Papers are solicited on theoretical approaches to electronic devices, including logic devices, memory devices, optical devices, interconnects and (bio)sensors. Theoretical approaches include analytical, numerical, statistical, and machine-learning/Al-based approaches applied to structures with dimensions ranging from atomistic over device dimensions to full-chip dimensions, including physics-based compact modeling. Key to submissions is, that the device innovation is central, either through predictive insight in the potential of novel device concepts, predictive analysis revealing significant improvement to devices, breakthroughs in the theoretical understanding of the device operation, breakthroughs in the understanding of device processing enabling improved device performance, novel insights in variability, reliability and yield issues, breakthrough in device optimization based on DTCO. Topics also include ab-initio/atomistic materials modeling, modeling of neuromorphic computing, quantum computing, spintronics, low-dimensional devices, ferroelectrics, thermal modeling, 3D/heterogeneous integration, electro-chemical/mechanical devices. Comparison with experimental data, model calibration and multi-scale simulation chains are highly encouraged.

### **NEUROMORPHIC COMPUTING (NC):**

Papers are solicited in the areas related to devices, circuits, and algorithms for neuromorphic computing and Al. We welcome submissions covering a wide range of areas in neuromorphic computing including but not limited to: analog in-memory deep learning, compute-in-memory, probabilistic/approximate/analog computing, combinatorial optimization, machine learning, and Al applications, edge computing, unclonable functions, reservoir computing, spiking neural network, artificial intelligence, in-sensor computing, and bio-inspired computing based on memory/logic/sensor/nanoelectronic/MEMS devices and their novel architecture and physics. Demonstration of real-world applications, full hardware integration, device-algorithm co-optimization, novel device concepts improving computational efficiency, and new algorithms mitigating non-ideal properties of devices and materials are of high interest.

## **OPTOELECTRONICS, DISPLAYS, and IMAGING SYSTEMS (ODI)**

Papers are solicited on optoelectronics, displays, and imaging systems. This includes novel devices, structures, and integration for image sensors, displays, light sources, photonic devices, and high-speed photodetectors and modulators. New technologies on heterogeneous integration of optoelectronics as well as on photonic-electronic integration for optical interconnects, on-chip networks and sensing are welcomed. Papers on quantum photonics, neuromorphic photonics, and plasmonics for quantum computation, sensing and encryption are also of interest. Furthermore, ODI includes CMOS imagers, high-speed and high-time resolution imagers, CCDs, stacked, single-photon and non-visible image sensors. In addition, papers on displays for augmented or virtual reality, holography, TFTs for photonics applications, flexible, stretchable, and/or printed electronics, in-display sensors are encouraged. Papers on displays or light emitting devices with novel materials such as perovskites or quantum dots are also of interest. We particularly welcome submissions concerning optoelectronic or photonic devices or systems based on topological concepts.

### POWER, MICROWAVE/MM-WAVE and ANALOG DEVICES/SYSTEMS(PMA)

Contributions are sought on novel circuit topologies, manufacturing processes, supporting modeling (TCAD and compact models), device physics, reliability, and materials (SiC, (Al)GaN, diamond, Ga2O3, Si, III-Vs, etc.) along with fundamental studies on doping, deep-level traps, interface state densities, and device reliability for power and/or high frequency devices. Papers are solicited on discrete and integrated power and/or high frequency (micro, mm-wave and THz) devices and physics, modules and systems. Topics of interest include devices (diodes, BJTs, FETs, super-junction devices, heterostructures, IGBTs, HEMTs, HBTs, light-triggered structures for galvanic isolation and faster switching, bi-directional switches, vertical geometry devices, etc.) and device/package/circuit interactions, including thermal management. Wide variety of applications are also of interest (power conversion, supply, regulation and conditioning for computers and data centers, motor drives, transportation, solar, wind, smart grid applications, wireless power harvesting/transfer, filters, beam formers, power amplifiers, tunable passives, antenna arrays, SAW/BAW).

## RELIABILITY OF SYSTEMS and DEVICES (RSD)

Papers are solicited in reliability evaluation (experimental and modeling) of logic and memory devices, interconnects, and circuits and systems, mainly (but not limited) to employing Si-based technologies. Specific reliability topics include, for FEOL: transistor degradation due to hot carriers, bias temperature instabilities, random telegraph noise, and aging model; dielectric SILC and wear-out. For MEOL/BEOL, topics include breakdown of MEOL spacers and BEOL dielectrics; electromigration, stress migration failures of contacts and interconnects. For product, system, and circuit reliability, topics include latch-up, ESD, soft error mechanisms, variability-aware design, and design for reliability, robustness, and security of electronic circuits and systems. Of particular interest are investigations of degradation mechanisms for devices, circuits, and systems in the following areas: conventional and emerging memories; beyond CMOS devices; 3D IC package reliability, more-than-Moore applications; biomedical devices and systems; automotive and aerospace.

## **SENSORS, MEMS, and BIOELECTRONICS (SMB)**

Papers are solicited in the areas of sensors, micro/nano electromechanical systems (MEMS and NEMS), microfluidics/lab-on-chip, and BioMEMS, with particular emphasis on new device concepts, integrated and highly parallel CMOS implementations, CMOS-on-MEMS, embedded machine learning, organic-inorganic hybrid microfabrication, flexible devices, and multimodal sensors on a chip for applications in health, medicine, communication, mobility, and energy. Sensors include chemical, molecular and biological detection based on acoustic, electrical, electrochemical, magnetic, mechanical and optical principles. Topics of interest in the MEMS area include actuators, physical and biochemical sensors (BioMEMS), resonators, integrated inertial measurement units, RF MEMS, optomechanical devices, micro-power generators, and devices for energy harvesting as well as on-chip energy storage. Bioelectronics covers organic-inorganic hybrid devices, point-of-care biomedical devices, bio-electronic interfaces, integrated biomedical sensing, and implantable sensors and neural interfaces.

## **Program**

### **Tutorials**

The tutorials are in their fourteenth year and are standalone presentations on specialized topics taught by world-class experts. These tutorials will provide a brief introduction to their respective fields and facilitate understanding of the technical sessions. In contrast, the traditional short courses are focused on a single technical topic.

All Tutorials will be held on Saturday, December 9, 2023.

#### **Tutorials**

Saturday, Dec. 9

Co-Chairs: Jean Anne Incorvia, University of Texas Austin

Dechao Guo, IBM and Gaudenzio Meneghesso, University of Padova

1:30 PM - 6:00 PM

Tutorial 1: Innovative Technology for Beyond 2 nm, Matthew Metz, Intel Corp.

1:30 PM– 2:50 PM Continental 4-5

Chair: Jean Anne Incorvia, University of Texas Austin

Intel is working at the forefront of revolutionary material and device improvements that the semiconductor industry needs to support continued performance improvements. This tutorial will focus on two of these research topics, Transition Metal Dichalcogenides for continued CMOS scaling and new materials and devices for ultra-low power computation.

Tutorial 2: CMOS+X: Functional Augmentation of CMOS for Next Generation Electronics, Sayeef Salahuddin, University of California, Berkeley

1:30 PM – 2:50 PM Continental 6-9

Chair: Dechao Guo, IBM

Despite ominous foretelling of a slowdown, over the last decade the computational throughput has increased by orders of magnitude. Energy efficiency is critical not only to maintain this incessant advancement, but also to ensure that electronics does not become a drag on the finite energy resources of the world. This will need a radical rethinking of the basic building blocks that constitute the electronic hardware. In this talk, I shall briefly present how integrated ferroelectric devices offer a new pathway in this context. First, I shall discuss the phenomenon of negative capacitance in ferroelectric materials. A fundamentally new state in the ferroelectric materials, negative capacitance promises to reduce power consumption in electronic devices significantly. I shall discuss our current understanding of negative capacitance derived from numerous experimental works done over the last few years. We shall further discuss the material science that is enabling the integration of negative capacitance into advanced transistors. Going beyond transistors, the insight gained from physics and materials could also lead to advanced, low power memory devices. Additionally, I shall present integrated magnetic devices. Beyond memory applications, these devices are showing promise for neuromorphic computing and sensing applications. These examples underscore how functional augmentation of CMOS by harnessing new physical phenomena, we are calling it CMOS+X, could offer opportunities that are otherwise not available through conventional means.

## Tutorial 3: Reliability Challenges of Emerging FET Devices, Jacopo Franco, imec

3:05 PM- 4:25 PM Continental 4-5

Chair: Jean Anne Incorvia, University of Texas Austin

The unabated performance enhancement of semiconductor technology has been sustained in recent years by disruptive device and material innovations. For the successful deployment of any novel device concept, the promised enhanced performance must be guaranteed for the entire expected lifetime of the final product. Traditionally, device reliability optimization was an aspect considered only at a late stage in the development of a new device technology. We argue that in contemporary devices, fabricated with complex integrations and a plethora of materials, potential reliability issues should be considered from the very early stage of the technology development, as they can potentially disqualify otherwise promising device concepts. In particular, charge trapping in gate dielectrics is an aspect that can "make or break" any MOS-based device, and thus gate stack stability should be considered as a primary metric in the evaluation of novel device concepts. In this Tutorial we will review the fundamentals of charge trapping in gate dielectrics in terms of phenomenology, characterization techniques and physical models. Next, we will briefly discuss as case studies some recent examples of MOS innovations which made it into mainstream technology (e.g., SiGe channels), as well as other examples which to date remain confined to academic research (e.g., III-V and Ge channels for Logic). We will then focus on specific gate stack challenges for upcoming CMOS technology innovations, including Nanosheet and Forksheet device architectures, and novel device concepts such as the stacked Complementary FET (CFET) and 2D channel transistors. To further highlight the general relevance of charge trapping in dielectrics, we will briefly discuss its role also in wide-bandgap semiconductors (GaN, SiC) MOS-based devices for Power and Analog/RF applications. Finally, we will discuss novel transistors based on oxide semiconductor channels (e.g., IGZO), which due to their extremely low off-state leakage and their flexible fabrication flow are considered as potential gamechangers for memory periphery and, in general, for the heterogeneous integration of transistors in the Back End of Line (BEOL). For these devices, we will discuss how the interplay between their gate dielectric and channel instabilities makes the reliability assessment and optimization particularly complex and requiring the combination of electrical and optical characterization techniques. 3:05 PM

**Tutorial 4: Advanced Packaging and Heterogeneous Integration - Past, Present & Future,** Madhavan Swaminathan, Penn State 3:05 PM – 4:25 PM Continental 6-9

Chair: Gaudenzio Meneghesso, University of Padova

The global semiconductor industry is projected to become a trillion-dollar industry by 2030. This is historic considering that it took the industry 55 years to reach half a trillion dollars in size and will take just another 10 years to double in size to a trillion dollars. Advanced packaging as it relates to heterogeneous integration will play an important role in making this happen. This tutorial will cover the fundamentals of advanced packaging covering the past and present state of the art including what is necessary in the future to enable heterogeneous integration. Metrics used to compare these technologies will be discussed.

## Tutorial 5: Synapses, Circuits, and Architectures for Analog In-Memory Computing-Based Deep Neural Network Inference Hardware Acceleration Irem Boybat, IBM Research Europe

4:40 PM - 6:00 PM

Continental 4-5

Chair: Jean Anne Incorvia, University of Texas Austin

The advent of deep neural networks (DNNs) has revolutionized numerous fields, including computer vision and natural language processing. These powerful models have showcased remarkable capabilities in solving complex problems, but their training and inference procedures often require significant computational resources. To address this challenge, notable activity was centered around specializing or developing digital hardware accelerators for DNNs, such as graphics processing units (GPUs) and tensor processing units (TPUs). However, this talk will go beyond digital acceleration and instead focus on the emerging field of analog in-memory computing (AIMC). More specifically, it will delve into devices, synapses, circuits, and architectures for building energy efficient yet accurate AIMC-based accelerators for DNNs. We will explore how the AIMC paradigm can overcome the limitations of traditional digital computing approaches and offer better energy efficiency by blurring the distinction between memory and computing. We will investigate the impact of device characteristics and their organization into synapses on DNN inference and training accuracies. Furthermore, we will discuss the role of peripheral circuits and accelerator architectures on energy efficiency and performance.

## Tutorial 6: Tools for Device Modeling: From SPICE to Scientific Machine Learning, Keno Fischer, JuliaHub, Inc.

4:40 PM - 6:00 PM

Continental 6-9

Chair: Gaudenzio Meneghesso, University of Padova

How do we know if our devices will work before we tape them out? Since the dawn of the semiconductor industry, modeling and simulation has been a cornerstone of both process development and pre-tapeout verification. And yet, despite this rich heritage, some of the most impactful capabilities remain underutilized or locked away in hard-to-use, bespoke tools. In this tutorial, we will take a look at the modeling modalities available for semiconductor devices, from our venerable compact MOSFET models, through TCAD, down to direct Density Functional Theory calculations. We will explore how we can leverage these models beyond simple simulation for device optimization, characterization, model calibration and more. Then, we will turn to more recent techniques, exploring how Scientific Machine Learning allows the creation of multi-scale surrogate models at tunable fidelity and performance. Finally, we will look at our real-world experiences developing CedarEDA and vision for the future of device modeling and how we can bring advanced modeling closer to engineering practice to reduce the costly iterations, build better devices, and improve our engineering productivity.

### **Short Courses**

IEEE IEDM will offer two short courses with in-depth coverage of highly relevant topics from world experts. All short courses will be held on Sunday, December 10.

## Short Course 1: Transistor, Interconnect, and Chiplets for the Next Generations of Low-Power & High-Performance Computing

9:00 AM, Continental 4-5

Co-Chairs: Yuri Masuoka, Samsung and Dechao Guo, IBM

9:00 AM

## 1-1 Advanced Technology Requirement for Edge Computing, Jie Deng, Qualcomm

The next-generation computing market is poised to experience an astounding six-fold surge from 2023 to 2033, driven by a remarkable compound annual growth rate (CAGR) exceeding 19% in the next decade. The escalating computing demand intensifies the necessity for optimal low-power and high-performance solutions. Achieving continuous power-performance scaling demands seamless synergy between transistors, interconnects, and packaging technologies. With FinFET scaling approaching its limits, innovative device architectures emerge as promising candidates for next-generation transistor technology, including gate-all-around (GAA/NS), Forksheet FET (FS), complementary FET (CFET), 2D-material FET. To address large wire delay and the high IR drop issue resulting from continuous area scaling, novel interconnect material and innovative integration schemes like Backside Power Delivery (BSP) are required. Furthermore, the semiconductor industry is moving towards advanced heterogeneous packaging platforms for both 2.5D and 3D integration. In this short course, we will explore the current state of transistor, interconnect, and packaging technologies, review challenges in continuous power-performance scaling, and delve into emerging technologies for next-generation low-power, high-performance computing. Additionally, we will discuss economic impact and production interception timeline outlook of various emerging technologies for different applications.

#### 10:40 AM

### 1-2 Process Technology Towards 1nm and Beyond, Tomonari Yamamoto, <sup>1</sup>TEL

This short course will cover the processes technologies that enable the continuous evolution of logic transistors and interconnects towards the 1nm node and beyond. The critical metric for logic density is the product of the "logic cell width x logic cell height". Gate pitch scaling is a crucial factor for scaling logic cell width. To enable this, scaling of gate length, gate spacer width, and contact feature size is necessary. Gate-All-Around (GAA) technology improves electrostatics compared to FinFETs and enables continuous gate length scaling. Material advancements are necessary to mitigate parasitic capacitance and resistance increase while securing yield and reliability of the transistors. In terms of the logic cell height, advancements in layout and transistor structure innovations, as well as interconnect metal pitch scaling, contribute to its scaling. Continuous RC reduction techniques have been implemented for copper interconnect extension with metal pitch scaling. Eventually, alternative metals that outperform copper in CD sizes of 10nm and below need to be considered. Regarding layout and transistor structure innovations, a backside Power Delivery Network (PDN) is an attractive option for better area utilization and performance enhancement. Additionally, Complementary FET (CFET), which consists of stacked transistors, is a promising architecture for enabling continuous logic cell height scaling. To enable these advancements, continuous process and tool advancements are necessary not only in film, etch, lithography, and wet processing but also in wafer bonding and thinning technologies. The talk will also review recent progress in EUV-related solutions, including self-aligned patterning.

#### 1:10 PM

## 1-3 Empowering Platform Technology with Future Semiconductor Device Innovation, Jaehun Jeong, Samsung

FinFET, the platform technology in foundry business for more than a decade, has faced fundamental limitations for the further scaling with PPA improvement and it is the time to move on another "New dimension" of transistor. Gate-All-Around (GAA) FETs / MBCFETTM have been already introduced as the logic device for next generation and started mass production. MBCFETTM has been enabling different type of PPA enhancement with the design flexibility allowing additional room for DTCO to optimize standard cell speed/power with various nano-sheet size beyond its intrinsic device gain like short channel effect improvement and high drivability. In the near future, 3D stacked structure connecting multiple layers of transistors vertically and Backside-PDN technology relocating the power delivery network to the backside of the chip will be ready for innovative integration schemes. Also, 2D transistor has been studied to use their high

carrier mobility and excellent electrostatic control enabling another scaling of gate length and pitch. These innovations in the semiconductor industry can bring another breakthrough to enhance the capabilities of foundry platform technologies, and the key to sustainable success lies in how to harness the power of those technological advancement to the platform technology including emerging applications such as mobile SoC, Al, autonomous vehicle and HPC with enhancement of overall chip performance.

#### 2:25 PM

## 1-4 Future Power Delivery Process Architectures and Their Capability and Impact on Interconnect Scaling, Kevin Fischer, Intel Corporation

As continued semiconductor technology scaling becomes increasingly more challenging and expensive it is crucial to invent ways to enable increasing the ability to interconnect the transistors and slow the degradation of the interconnect properties. Traditionally, degree of connectivity is maintained thru scaling interconnect pitches and feed thru pitches and adding ever more interconnect layers. The cost of this approach is becoming increasingly more impactful we must find new ways to add design value and scaling capability outside of the conventional approach. Novel technologies such as buried power rails can reduce the impact of these effects to a limited extent. One step beyond this lies in the introduction of backside power. Moving power to the backside of the wafer greatly reduces the interconnect tax on the conventional front side interconnects by removing the need spend interconnect resources on power. Beyond backside power advantage lies in leveraging the ability to contact the transistor from top and bottom and introducing dense metal on both frontside and backside. In this short course we will look at the scaling pressures on interconnects driving the need for these new technologies as well as the technologies themselves along with the engineering opportunities and challenges for high volume manufacturing.

#### 4:05 PM

## 1-5 DTCO/STCO in the Era of Vertical Integration, Y.K. Chong, ARM Ltd.

As we venture into the era of AI, the demand for energy-efficient computation continues to accelerate. However, the relentless push towards smaller semiconductor geometries has brought about significant challenges to technology scaling. To sustain progress, the semiconductor industry must explore alternative approaches. Coordinated innovations across system, circuit, and technology abstraction levels are needed to continue the trajectory of power, performance, area, and cost (PPAC) metrics within compressed product development timelines. In this short course, we offer an industry perspective on the technological and product development challenges of advanced process nodes. We will delve into Design-Technology Co-Optimization (DTCO) and System-Technology Co-Optimization (STCO) strategies that have been explored at Arm, encompassing various techniques applied to logic, SRAM, interconnects, power delivery, system partitioning, and packaging. We hope that our practical insights will help device engineers, circuit designers, and system architects to continue to improve high-performance computing in the sub-3 nm era.

### 5:20 PM

## **1-6 Low Power SOC Design Trends/3D Integration/Packaging for Mobile Applications, Milind Shah, Google**

Moore's Law has been the driving force behind the scaling of process nodes for decades, enabling higher transistor density in monolithic system-on-chip (SoC) architecture designs. However, cost pressure and longer cycle times for manufacturing monolithic SoC designs in recent process generations have slowed down node scaling, forcing chip designers to explore new architectures to meet higher performance requirements more economically. Chiplet-based architectures with high-density interconnect packaging integration for homogeneous and/or heterogeneous nodes offer a new way to design chips that allow for more flexibility and scalability, as well as the creation of chiplets tailored to specific applications and easier upgrades. This short course will review the current industry landscape of 3D packaging integration solutions, which enable higher off-chip interconnect density, resulting in higher data bandwidth, power efficiency, lower data communication latency and future trends. The broader industry trend of 3D interconnect packaging strategy and optimization will also be highlighted in this study.

**Short Course 2: The Future of Memory Technologies for High-Performance Memory and Computing** 9:00 AM, Continental 6-9

Co-Chairs: Ki-il Moon, SK Hynix and Gaudenzio Meneghesso, University of Padova

#### 9:00 AM

## **2-1 High-Density and High-Performance Technologies for Future Memory**, Koji Sakui, Unisantis Electronics Singapore/Tokyo Institute of Technology

The agenda is composed of four key technologies: 1) DFM, 2) KFBM, 3) SGT, and 4) BBCube. 1) DFM: A new high-density memory technology called Dynamic Flash Memory (DFM) which can be built using a conventional silicon process. DFM is scalable and has no special material requirements, making it a cost-effective alternative to emerging memory technologies. The proposed stackable DFM eliminates the need for capacitors, resulting in smaller cell sizes than 6F² with 3~4 tiers. 2) KFBM: A fully CMOS compatible Key shape Floating Body Memory (KFBM) cell consists of MOSFET with virtually floating body formed by bulk silicon and trench with on/off margins of more than three orders of magnitude. The vertical device in KFBM helps to improve retention and disturbance and reduce the scaling pressure. 3) SGT: A Surrounding Gate Transistor (SGT) has advantages of improved density and reduced power leakage, which means that the SGT is a promising candidate for a switching transistor of a variety of memory devices, such as DRAM. 4) BBCube: The Bumpless Build Cube (BBCube) 3D has been proposed for Al and HPC applications, which need high bandwidth and power efficiency. The BBCube 3D is constructed by heterogeneous 3D integration in which xPU (CPU, GPU etc.) chips and DRAM wafers are stacked using a combination of bumpless Wafer-on-Wafer and Chip-on-Wafer. The BBCube 3D has the potential to achieve a bandwidth 30 times higher than DDR5 and four times higher than HBM2E with the access energy per bit 1/20th that of DDR5 and 1/5th that of HBM2E.

#### 10:30 AM

## 2-2 Advanced Packaging Solutions for High Performance Memory and Compute, Jaesik Lee, SK Hynix USA

Generative AI such as ChatGPT and Bard, which are based on large language models capable of producing human like text and images, have becomes mainstream for artificial intelligence technology industries. In order to run the increased model sizes without performance degradation, a large amount of memory needs to be integrated in a system. High bandwidth memory (HBM) is a perfect solution to meet the system requirements like high bandwidth and low power consumption together with concurrent integrations of the logic chips in 2.5D and 3D advanced packaging technologies. 5th generation HBM, HBM3E, has been developed since HBM1 was produced in 2013. The continued scaling of HBM to increase memory capacity and to enhance thermal performance necessitates the evolutions of 3D stacking technologies. In this short course, we will talk on the HBM stacking innovations and their challenges associated with advance packaging technologies. In addition, how to ensure that HBM is compatible to packaging processes and reliability in advanced packaging technologies such as CoWoS-S and CoWoS-L will be presented. HBM challenges associated with system level cooling integration will be also presented.

### 12:45 PM

2-3 Analog In-Memory Computing for Deep Learning Inference, Abu Sebastian, IBM Research - Zurich Deep neural networks (DNNs) are revolutionizing the field of artificial intelligence and are key drivers of innovation in device technology and computer architecture. While there has been significant progress in the development of specialized hardware for DNN inference, many of the existing architectures physically split the memory and processing units. This means that DNN models are typically stored in a separate memory location, and that computational tasks require constant shuffling of data between the memory and processing units – a process that slows down computation and limits the maximum achievable energy efficiency. Analog in-memory computing (AIMC) is a promising approach that addressing this challenge by borrowing two key features of how biological neural networks are realized. Synaptic weights are physically localized in nanoscale memory elements and the associated computational operations are performed in the analog/mixed-signal domain. In the first part of the course, I will introduce AIMC based on non-volatile memory technology. The focus will be on the key concepts and the associated terminology. Subsequently, a multi-tile mixed-signal AIMC chip for deep learning inference will be presented. This chip fabricated in 14nm CMOS technology comprises 64 AIMC cores/tiles based on phase-change memory technology. It will serve as the basis to delve deeper into the device, circuits, architectural and algorithmic aspects of AIMC. Of particular focus will be achieving floating point-equivalent classification accuracy while performing the bulk of computations in the analog domain with

relatively less precision. I will also present an architectural vision for a next generation AIMC chip for DNN inference. I will conclude with an outlook for the future.

#### 2:00 PM

## 2-4 Key Challenges and Directional Path of Memory Technology for Al and High-Performance Computing, Keith Kim,NVIDIA

Al/ML continues to evolve beyond inferencing and training the image. Especially Generative Al unlocks new possibilities for all industries and larger language model is to accelerate computing resources, driving memory performance and density while focusing on energy efficiency. In addition, security and memory RAS cannot be ignored since data center data integrity is one of key technologies in data center. This short course will address the directional path of memory technology requested by Al/HPC applications, and technical challenges for bandwidth, power, density, RAS, and security. Both barriers and potential technology solutions will be reviewed. Towards resolving memory walls and meeting system requirements, initiatives to develop new memory technologies for Al/HPC are needed.

## 3:30 PM

## 2-5 The Next Generation of Al Architectures: The Role of Advanced Packaging Technologies in Enabling Heterogeneous Chiplets, Raja Swaminathan, AMD

As we further race to bring together heterogenous compute and acceleration from the motherboard to the package, our industry will need to solve several new challenges. Chiplet architectures are fundamental to the continued economic viable growth of power efficiency of AI, 5G and edge computing. The slowing of Moore's law has also placed advanced packaging at the critical juncture of technology-architecture intersection driving unique product capabilities. UCle is a great step forward to address the interconnect aspect, but how do we bring UCle together with advanced packaging. What standard form factors should we define? How do we enable debug/test beyond KGD? What kind of power delivery and thermal controls will we need? Can we also enable DVFS and binning? How do these challenges differ between advanced and organic packaging solutions? In this course, we will take a look at these questions and discuss some possible ways forward to address these challenges. New heterogeneous architectures like 2.5D Fanout and 3D Hybrid bonded architectures driving AMD's industry leading advanced technology roadmap to enable power, performance, area, and cost (PPAC) as well as challenges and solutions for large chiplet modules etc. will also be discussed.

#### 4:45 PM

2-6 Charge-Trapping Memories: From the Fundamental Device Physics to 3D Memory Architectures (3D NAND, 3D NOR, 3D DRAM) and Computing in Memory (CIM), Hang-Ting (Oliver) Lue, Macronix Charge-trapping Flash memory devices, including SONOS and its variations, have surpassed floating gate (FG) devices in the commercial market share recently, primarily due to the remarkable success of 3D NAND technology. This concise course will commence with a review of the fundamental physical principles behind bandgap engineered (BE) SONOS, encompassing AB initio modeling of commercially adopted SiON tunnel dielectrics and SiN traps. Detailed scrutiny will extend to 3D NAND architectures, encompassing both standard commercial cells and emerging double-density structures such as hemi-cylindrical or flat cells. Additionally, the potential of 3D NOR structures to offer a superior product performance with low-latency and byte-addressable 3D memory will be explored. Introducing a notable innovation, a micro heater capable of localized heating above 400°C will be presented. This innovation has potential to enhance the P/E cycling endurance of 3D charge-trapping Flash memory to over 100 million cycles, with remarkable high-temperature data retention. Finally, addressing the escalating demands of big-data Al computing, the course will delve into 3D DRAM architectures and the concept of computing in memory (CIM) utilizing 3D memory technology.

#### **Welcome and Awards Presentations**

Monday, Dec. 11

Session 1: Welcome and Awards Presentations

Dina Triyoso, TEL Technology Center, America, LLC

General Chair

9:00 AM, Grand Ballroom B

#### 2023 IEEE Andrew S. Grove Award

Awarded to Hon-Sum Philip Wong

"For contributions to novel and advanced semiconductor device concepts and their implementation"

### 2022 Roger A. Haken Best Student Paper Award

Awarded to Ruben Asanovski

For the paper entitled, "New insights on the excess 1/f noise at cryogenic temperatures in 28 nm CMOS and Ge MOSFETs for quantum computing applications"

### **2022 EDS Paul Rappaport Award**

To: Akshay Arabhavi, Filippo Ciabattini, Sara Hamzeloui, Ralf Flückiger, Tamara Saranovac, Daxin Han, Diego Marti, Giorgio Bonomo, Rimjhim Chaudhary, Olivier Ostinelli, and Colombo R. Bolognesi

For the paper entitled: "InP/GaAsSb Double Heterojunction Bipolar Transistor Emitter-Fin Technology With fMAX = 1.2 THz "

### **2022 EDS George Smith Award**

To: Sourav De, Franz Müller, Nellie Laleni, Maximilian Lederer, Yannick Raffel, Shaown Mojumder, Alptekin Vardar, Sukhrob Abdulazhanov, Tarek Ali, Stefan Dünkel, Sven Beyer, Konrad Seidel, and Thomas Kämpfe For the paper entitled: "Demonstration of Multiply-Accumulate Operation With 28 nm FeFET Crossbar Array"

### 2022 EDS Leo Esaki Award

**To:** Fei Mo, Jiawen Xiang, Xiaoran Mei, Yoshiki Sawabe, Takuya Saraya, Toshiro Hiramoto, Chun-Jung Su, Vita Pi-Ho Hu, and Masaharu Kobayashi

**For the paper entitled:** "Efficient Erase Operation by GIDL Current for 3D Structure FeFETs With Gate Stack Engineering and Compact Long-Term Retention Mode"

### 2023 EDS Distinguished Service Award

To: Fernando Guarin, Retired, NY, USA

"For Outstanding and Dedicated Service for the Benefit and Advancement of the Electron Devices Society"

### **2023 EDS Education Award**

**To:** Gary S. May, University of California, Davis, CA, USA "For dedicated leadership and mentorship that has diversified academic leaders in education"

### 2023 EDS Lester F. Eastman Award

**To:** James C. Hwang, Cornell University, Ithaca, NY, USA "For outstanding achievement in high-performance semiconductor devices"

### 2023 EDS J.J. Ebers Award

**To:** Mukta Farooq, IBM, Hopewell Junction, NY, USA "For development of emerging heterogeneous integration architectures for 3D ICs"

### **2023 IEEE/EDS Fellows**

\*This is a complete listing of the 2023 IEEE/EDS Fellows. Not all Fellows will be recognized at the 2023 IEDM

**Shekhar Bhansali** - for contributions to portable realtime sensing devices for continuous monitoring **Kyung Cheol CHOI** - for contributions to emissive, flexible, and wearable displays **Tetsuo Endoh** - for contributions to nonvolatile memory and spintronic logic **Harald Gossner** - for contributions to ESD design of advanced IC devices and high speed systems

Masataka Higashiwaki- for contributions to gallium oxide electronics and milimeter-wave gallium nitride transistors

Andras Kis - for contributions to the development of 2D materials and electronic devices

**Guann-pyng Li** - for contributions to the bipolar device, circuit and technology in silicon and compound semiconductors

**Takashi Matsuoka** - for contributions to laser diodes for optical communications and nitride semiconductors for light emitting devices

**Thomas Mikolajick** - for contributions to nonvolatile memory

Yoshiaki Nakano - for contributions to semiconductor integrated photonic devices and circuits

Kenichi Okada - for contributions to millimeter-wave communication circuits design

Boon S. Ooi - for contributions to broadband light emitters and visible light communications

**Guann Pyng Li** - for contirbutions to the bipolar device, circuit and technology in silicon and compound semiconductors

Munaf T Rahimo - for contributions to high-voltage insulated gate bipolar transistors for grid applications

Sei-Hyung Ryu - for contributions to silicon carbide power device technology

Abu Sebastian - for contributions to in-memory computing for scientific applications

**Dmitri Strukov** - for contributions to neuromorphic and alternative computing systems based on emerging memory devices

**Richard Syms -** for contributions to mass spectrometers based on microelectromechanical system technology **Miguel Urteaga** – for contributions to terahertz heterojunction bipolar transistor integrated circuit technology **Pierre Verlinden** - for leadership in high performance silicon solar cell and photovoltaics technology and commercialization

**Hua Wang** - for contributions to high-efficiency microwave and millimeter-wave power amplifiers **Qiangfei Xia** - for contributions to resistive memory arrays and devices for in-memory computing

## **Plenary Papers**

Technical Program Chair: Kirsten Moselund, Paul Scherrer Institute (PSI) / EPFL

9:30 AM

**1-1** Redefining Innovation: A Journey forward in New Dimension Era (Invited), Siyoung Choi, President and GM Foundry Business, Device Solutions Division, Samsung Electronics

The semiconductor industry has been experiencing drastic changes of the surrounding economic and geopolitical circumstances, and it has become more essential because of its permeating role in numerous other industries. In particular, the incessant foundry progress has been maintained through a series of fundamental technology breakthroughs from materials to structures, taming several complicated difficulties associated with technical and cost barriers. The track records set by foundries' technology developments are clear for all to see, and their positive impact on our lives is immeasurable.

10:20 AM

**1-2 Making Memory Magic and the Economics Beyond Moore's Law (Invited)**, Thy Tran, Vice President of Global Frontend Procurement, Micron Technology

The global semiconductor industry, driven by compute, automotive, data storage, and wireless markets, is projected to exceed a trillion-dollar in sales revenue by 2030 (Fig. 1), [1]. The mainstream memory industry bit shipment has increased by 12x for DRAM and 48x for NAND flash in the past decade [2] and this bit growth trend needs to be sustained through continued scaling in the future to meet the projected demands of global data creation (Fig. 2). In addition, generating value from the data is driving the need for memory to be closer to the compute and increase data bandwidth, speed, and energy per bit metrics. Delivering higher bandwidth and speed at lower energy while minimizing power has become a major challenge with respect to continued scaling of memory, which also must deliver year over year cost reduction at faster cadence. In this paper, we touch on

DRAM and NAND scaling challenges and industry trends to tackle the power, performance, area, cost, and time (PPACt) requirements through design and technology co-optimization (DTCO). Such requirements are also driving memory development to explore advanced interconnect and innovative packaging solutions.

### 11:10 AM

**1-3** Semiconductor Challenges in the 5G and 6G Technology Platforms (Invited), Bjorn Ekelund Corporate Research Director, <sup>1</sup>Ericsson AB, Sweden

The global semiconductor industry, driven by compute, automotive, data storage, and wireless markets, is projected to exceed a trillion-dollar in sales revenue by 2030 (Fig. 1), [1]. The mainstream memory industry bit shipment has increased by 12x for DRAM and 48x for NAND flash in the past decade [2] and this bit growth trend needs to be sustained through continued scaling in the future to meet the projected demands of global data creation (Fig. 2). In addition, generating value from the data is driving the need for memory to be closer to the compute and increase data bandwidth, speed, and energy per bit metrics. Delivering higher bandwidth and speed at lower energy while minimizing power has become a major challenge with respect to continued scaling of memory, which also must deliver year over year cost reduction at faster cadence. In this paper, we touch on DRAM and NAND scaling challenges and industry trends to tackle the power, performance, area, cost, and time (PPACt)requirements through design and technology co-optimization (DTCO). Such requirements are also driving memory development to explore advanced interconnect and innovative packaging solutions.

### **Technical Sessions**

## Session 2: Advanced Logic Technology (ALT) - Gate-All-Around and New Channel Material Devices 1:30 PM, Grand Ballroom A

Co-Chairs: Anne Vandooren, IMEC and Byounghak Hong, Samsung

This session covers recent advances in 2D transition metal dichalcogenide (TMD) and gate-all-around (GAA) devices to further extend Moore's law, consisting of six papers both from industry and academia. Two papers highlight 2D channel material devices. The first paper focuses on MoS2 single channel performance optimization and demonstrates 2 -monolayer stacked channels formation thanks to highly selective channel release. The second paper addresses manufacturability of 2D materials at 300mm wafer scale. The next three papers focus on Si nanosheet GAA transistors. The first one is an invited paper which identifies challenges to further scale GAA devices from a patterning perspective with EUV insertion. The second one demonstrates the performance benefits of a nanosheet technology optimized for a 77K operating temperature. The third paper is a systematic study of the impact of Si (001) and (110) orientation on nanosheet NFET and PFET showing an overall better performance on (001) substrate orientation. The last paper of the session presents a new fabrication process of GeOI FinFETs based on layer transfer to eliminate channel defects and maximize device performance at 10K.

#### 1:35 PM

**2-1** Monolayer-MoS<sub>2</sub> Stacked Nanosheet Channel with C-type Metal Contact, Yun-Yan Chung<sup>1</sup>, Wei-Sheng Yun<sup>1</sup>, Bo-Jhih Chou<sup>2</sup>, Chen-Feng Hsu<sup>1</sup>, Shao-Ming Yu<sup>1</sup>, Goutham Arutchelvan<sup>1</sup>, Ming-Yang Li<sup>1</sup>, Tsung-En Lee<sup>1</sup>, Bo-Jiun Lin<sup>1</sup>, Chen-Yi Li<sup>2</sup>, Aslan Wei<sup>1</sup>, D. Mahaveer Sathaiya<sup>1</sup>, Cheng-Ting Chung<sup>1</sup>, San-Lin Liew<sup>1</sup>, Vincent D.-H. Hou<sup>1</sup>, Wen-Hao Chang<sup>3</sup>, Bo-Heng Liu<sup>4</sup>, Chien-Wei Chen<sup>4</sup>, Chien-Ying Su<sup>4</sup>, Chi-Chung Kei<sup>4</sup>, Jin Cai<sup>1</sup>, Chung-Cheng Wu<sup>1</sup>, Jeff Wu<sup>1</sup>, Tung-Ying Lee<sup>1</sup>, Chao-Hsin Chien<sup>2</sup>, Chao-Ching Cheng<sup>1</sup>, Iuliana P. Radu<sup>1</sup> Taiwan Semiconductor Manufacturing Company, Hsinchu, Taiwan, <sup>2</sup>Institute of Electronics National Yang Ming Chiao Tung University, Hsinchu, Taiwan, <sup>3</sup>Department of Electrophysics National Yang Ming Chiao Tung University, Hsinchu, Taiwan, <sup>4</sup>Taiwan Instrument Research Institute, National Applied Research Laboratories, Hsinchu, Taiwan

First demonstrates stacked-nanosheet-devices with 1L-MoS<sub>2</sub> after release 2 nanosheets simultaneously. Two-stacked 1L-MoS<sub>2</sub> nanosheets can be released 150nm, proving excellent mechanical properties. Conformal-gate-stack-deposition on 2-stacked MoS<sub>2</sub>-sheets is confirmed. 'C-type' wrap-around-contact is demonstrated

for contact-area-increasing. First time, gate-stack and its impact on SS, Vth and hysteresis are presented on single-GAA-NSFET with postive-Vth.

### 2:00 PM

## 2-2 Exploring manufacturability of novel 2D channel materials: 300 mm wafer-scale 2D NMOS & PMOS using MoS<sub>2</sub>, WS<sub>2</sub>, & WSe<sub>2</sub>

Chelsey Dorow<sup>1</sup>, Tom Schram<sup>2</sup>, Quentin Smets<sup>2</sup>, Kevin O'Brien<sup>1</sup>, Kirby Maxey<sup>1</sup>, Chia-Ching Lin<sup>3</sup>, Luca Panarella<sup>2,4</sup>, Ben Kaczer<sup>2</sup>, Nazmul Arefin<sup>1</sup>, Anandi Roy<sup>3</sup>, Rob Jordan<sup>5</sup>, Adedapo Oni<sup>5</sup>, Ashish Penumatcha<sup>1</sup>, Carl Naylor<sup>1</sup>, Mahmut Kavrik<sup>1</sup>, Daire Cott<sup>2</sup>, Benjamin Groven<sup>2</sup>, Valeri Afanasiev<sup>2,4</sup>, Pierre Morin<sup>2</sup>, Inge Asselberghs<sup>2</sup>, Cesar Lockhart de la Rosa<sup>2</sup>, Gouri Sankar Kar<sup>2</sup>, Matthew Metz<sup>3</sup>, Uygar Avci<sup>3</sup>, Intel, <sup>2</sup>IMEC, <sup>3</sup>Components Research, Intel Corporation, <sup>4</sup>KU Leuven, <sup>5</sup>Intel Corporation

We scale up to 300 mm both NMOS and PMOS 2D transistors using today's leading TMD candidates:  $MoS_2$ ,  $WS_2$ , and  $WSe_2$ .  $MoS_2$  outperforms  $WS_2$  for NMOS while  $WSe_2$  multi-layers show high PMOS on-currents reaching 200  $\mu$ A/ $\mu$ m. Larger TMD grain sizes show up to 10× higher on-currents and steeper SS.

### 2:25 PM

**2-3** Scaling opportunities for Gate-All-Around and beyond: A patterning perspective (Invited) Indira Seshadri<sup>1</sup>, Eric Miller<sup>1</sup>, Jennifer Church<sup>1</sup>, Jingyun Zhang<sup>1</sup>, Andrew Greene<sup>1</sup>, Julien FROUGIER<sup>1</sup>, Tao Li<sup>1</sup>, Yasiel Cabrera<sup>1</sup>, Martin Burkhardt<sup>1</sup>, Spyridon Skordas<sup>1</sup>, Luciana Meli<sup>1</sup>, Nelson Felix<sup>1</sup> IBM

Here, we review how EUV (extreme ultraviolet) lithography especially in the front end of line simplifies gate all around fabrication. We discuss avenues to the further scaling of GAA - High Numerical Aperture (NA=0.55) EUV and chiplet integration.

#### 2:50 PM

## 2-4 High Performance Nanosheet Technology Optimized for 77 K

Ruqiang Bao<sup>1</sup>, Liqiao Qin<sup>2</sup>, Julien FROUGIER<sup>2</sup>, Sung Dae Suk<sup>2</sup>, Mohamed Rabie<sup>2</sup>, Utkarsh Bajpai<sup>2</sup>, Anthony Chou<sup>2</sup>, Bettina Nechay<sup>3</sup>, Mohamed Mohamed<sup>4</sup>, Ruturaj Pujari<sup>2</sup>, Terence Weir<sup>4</sup>, Karen Harmon<sup>4</sup>, Aditya Varma<sup>4</sup>, Wayne Armstrong-Moore<sup>3</sup>, Alberto Cestero<sup>2</sup>, Susan Emans<sup>2</sup>, Prateek Hundekar<sup>2</sup>, R Joshi<sup>2</sup>, Juntao Li<sup>2</sup>, Xuan Liu<sup>2</sup>, Steve Lucarini<sup>2</sup>, Carl Radens<sup>2</sup>, Shahab Siddiqui<sup>2</sup>, Henry Trombley<sup>2</sup>, Andres Bryant<sup>2</sup>, Mohammad Hasanuzzaman<sup>2</sup>, Amlan Majumdar<sup>2</sup>, Min Gyu Sung<sup>2</sup>, Jingyun Zhang<sup>2</sup>, Effendi Leobandung<sup>2</sup>, <sup>1</sup>IBM Research, <sup>2</sup>IBM, <sup>3</sup>Northrop Grumman, <sup>4</sup>MIT Lincoln Laboratory

We demonstrated high performance Nanosheet technology at 77 K with dual work function metals (WFMs) and dual dipoles at 77 K. Nanosheet with low  $V_{DD}$  (0.3 - 0.4 V) at 77 K provides comparable performance to that at 300K with  $V_{DD}$ =0.75V, but at much lower power.

## 3:40 PM

## 2-5 Evaluation of (110) versus (001) Channel Orientation for Improved nFET/pFET Device Performance Trade-Off in Gate-All-Around Nanosheet Technology

Shogo Mochizuki<sup>1</sup>, Nicolas Loubet<sup>1</sup>, Pial Mirdha<sup>1</sup>, Curtis Durfee<sup>1</sup>, Huimei Zhou<sup>1</sup>, Gen Tsusui<sup>1</sup>, Julien FROUGIER<sup>2</sup>, Reinaldo Vega<sup>2</sup>, Liqiao Qin<sup>2</sup>, Nelson Felix<sup>2</sup>, Dechao Guo<sup>1</sup>, Huiming Bu<sup>1</sup>, IBM Research, <sup>2</sup>IBM

Stacked gate-all-around nanosheet (NS) pFET and nFET transistors have been fabricated on (110) and (001) substrates to determine the device performance dependence on Si channel orientation for short and long-channel NS devices.

### 4:05 PM

2-6 First Demonstration of Defect Elimination for Cryogenic Ge FinFET CMOS Inverter Showing Steep Subthreshold Slope by Using Ge-on-Insulator Structure

Xin-Ren Yu<sup>1</sup>, Chin-Cheng Hsieh<sup>2</sup>, Min-Hui Chuang<sup>3</sup>, Min-Yu Chiu<sup>4</sup>, Tsung-Chieh Sun<sup>2</sup>, Wei-Zhe Geng<sup>1</sup>, Wen-Hsin Chang<sup>5</sup>, Yu-Jen Shih<sup>1</sup>, Wen-Hsiang Lu<sup>1</sup>, Wei-Chieh Chang<sup>1</sup>, Yu-Chuan Lin<sup>1</sup>, Yu-Chia Pai<sup>1</sup>, Chia-Yen Lai<sup>6</sup>, Chiung-Yi Yang<sup>1</sup>, Yun Dei<sup>7</sup>, Nien-Chih Lin<sup>8</sup>, Hao-Yu Lu<sup>9</sup>, Ming-Han Chuang<sup>1</sup>, William Cheng-Yu Ma<sup>10</sup>, Chien-Ting Wu<sup>8</sup>, Kuo-Hsing Kao<sup>1</sup>, Darsen D. Lu<sup>1</sup>, Yao-Jen Lee<sup>8,11</sup>, Guang-Li Luo<sup>8</sup>, Meng-Hsueh Chiang<sup>1</sup>, Tatsuro Maeda<sup>5</sup>, Wen-Fa Wu<sup>8</sup>, Yi-Ming Li<sup>3</sup>, Tuo-Hung Hou<sup>8</sup>, Yeong-Her Wang<sup>1</sup>,

<sup>1</sup>Dept. of Electrical Engineering, National Cheng Kung University, <sup>2</sup>Academy of Innovative Semiconductor and Sustainable Manufacturing, National Cheng Kung University, <sup>3</sup>Institute of Communications Engineering, National Yang Ming Chiao Tung University, <sup>4</sup>Dept. of Electrical Engineering, National Sun Yat-Sen University, <sup>5</sup>National Institute of Advanced Industrial Science and Technology, <sup>6</sup>Institute of Artificial Intelligence Innovation, National Yang Ming Chiao Tung University, <sup>7</sup>Institute of Biomedical Engineering, National Yang Ming Chiao Tung University, <sup>8</sup>Taiwan Semiconductor Research Institute, <sup>9</sup>Intelligent Computing Industrial Doctorate Program, Miin Wu School of Computing, National Cheng Kung University, <sup>10</sup>Dept. of Electrical Engineering, Natl. Sun Yat-Sen University, <sup>11</sup>Institute of Pioneer Semiconductor Innovation, National Yang Ming Chiao Tung University

This work presents experimental electrical characteristics and circuit prediction at cryogenic temperatures for three different kinds of germanium (Ge)-based FETs with advanced Fin/GAA structures. Among them, the layer-transferred GeOI FinFET significantly improves its I-V characteristic during cryogenic measurements. The developed GeOI fabrication method provides an effective way to eliminate the defects originating from misfit dislocations at the Ge/Si substrate during epitaxial growth, which would be treated as the key to device performance enhancement under 10 K. According to the measured IV at 10 K and circuit prediction, GeOI FinFETs with high Ge crystallinity are strong candidates for High-Performance-Computing applications.

## Session 3: Modeling and Simulation (MS) - 2-D materials for advanced logic and quantum applications 1:30 PM, Grand Ballroom B

Co-Chairs: Devin Verreck, IMEC and Francois Triozon, CEA-Leti

The session includes 4 papers on the modeling of 2-D materials for advanced logic and quantum computing applications. The first 2 papers discuss conventional logic scaling, while the last 2 assess the potential of 2-D materials for quantum computing and spin logic. The first paper, by Gilardi and Zeevi of Stanford University, is a DTCO optimization of a dielectric barrier layer to improve EDP. The second paper, by Knobloch of TU Wien (invited), presents an overview of TCAD and compact model approaches to benchmark performance and reliability. The third paper, by Agashiwala of University of California Santa Barbara, evaluates 2-D materials for cryo-CMOS interface electronics in quantum computing, highlighting the advantages to conventional semiconductors. The fourth paper, by Zhang of University of California Santa Barbara, assesses 2-D materials for spin logic and interconnects, showing significant improvements in EDP and spin diffusion lengths.

### 1:35 PM

### 3-1 Barrier Booster for Remote Extension Doping and its DTCO in 1D & 2D FETs

Carlo Gilardi<sup>1</sup>, Gilad Zeevi<sup>1</sup>, Suhyeong Choi<sup>1</sup>, Sheng-Kai Su<sup>2</sup>, Terry Hung<sup>2</sup>, Shengman Li<sup>1</sup>, Nate Safron<sup>3</sup>, Qing Lin<sup>1</sup>, Tathagata Srimani<sup>1</sup>, Matthias Passlack<sup>3</sup>, Gregory Pitner<sup>3</sup>, Edward Chen<sup>2</sup>, Iuliana Radu<sup>2</sup>, H.-S. Philip Wong<sup>1</sup>, Subhasish Mitra<sup>1</sup>,

<sup>1</sup>Stanford University, <sup>2</sup>Taiwan Semiconductor Manufacturing Company Limited, Hsinchu, Taiwan, <sup>3</sup>Taiwan Semiconductor Manufacturing Company Limited, San Jose, CA, USA

We present *dielectric barrier booster* for remote extension doping in low-dimensional materials. Leveraging extensive DTCO, barrier booster enables 1.5× energy-delay product (EDP) benefits vs. no-barrier case. We derive insights and doping guidelines for Carbon Nanotube and MoS<sub>2</sub> FETs and we project 1.9× and 4.6× EDP benefits respectively vs. extension-undoped FETs.

## 2:00 PM

## 3-2 Modeling the Performance and Reliability of Two-Dimensional Semiconductor Transistors (Invited)

Theresia Knobloch<sup>1</sup>, Dominic Waldhoer<sup>1</sup>, Mohammad Davoudi<sup>1</sup>, Alexander Karl<sup>1</sup>, Pedram Khakbaz<sup>1</sup>, Manuel Matzinger<sup>1</sup>, Yichi Zhang<sup>2</sup>, Kirby K Smithe<sup>3</sup>, Aftab Nazir<sup>4</sup>, Chris Liu<sup>4</sup>, Yury Yuryevich Illarionov<sup>5</sup>, Eric Pop<sup>3</sup>, Hailin Peng<sup>2</sup>, Ben Kaczer<sup>6</sup>, Tibor Grasser<sup>1</sup>.

<sup>1</sup>TU Wien, <sup>2</sup>Peking University, <sup>3</sup>Stanford University, <sup>4</sup>Huawei Technologies R&D, <sup>5</sup>SUSTech University, <sup>6</sup>IMEC

2D materials offer high mobilities and drive currents in atomically thin layers, allowing for excellent gate control. To enable the transition from prototypes to integrated circuits at an industrial scale, physical predictive modeling tools are required. We show how TCAD and compact models can be used to describe the performance.

### 2:25 PM

# **3-3** Advancing High-performance Large-Scale Quantum Computing with Cryogenic 2D-CMOS Kunjesh Agashiwala<sup>1</sup>, Arnab Pal<sup>1</sup>, Hang Cui<sup>1</sup>, Tanmay Chavan<sup>1</sup>, Wei Cao<sup>1</sup>, Kaustav Banerjee<sup>1,</sup> <sup>1</sup>UC Santa Barbara

This paper provides the first comprehensive insight into 2D-semiconductors (2DS) as a cryogenic-CMOS-interface-electronics platform to enable large-scale quantum-computing. Using rigorous ab-initio and transport simulations, we demonstrate that 2DS-FETs operate at ultralow supply-voltages with minimal noise introduced to qubits along with significantly reduced device-to-device mismatch, leading to unmatchable energy-efficiency and performance.

#### 2:50 PM

## 3-4 A Materials-Device Co-Design Framework for Realizing Ultra Energy-Efficient All-2D-Spin-Logic Circuits with 2D-Materials

Shuo Zhang<sup>1</sup>, Arnab Pal<sup>2</sup>, Wenyan Yin<sup>1</sup>, Wei Cao<sup>2</sup>, Kaustav Banerjee<sup>2</sup>, <sup>1</sup>Zhejiang University, <sup>2</sup>University of California, Santa Barbara

This work introduces a materials-device co-design framework for optimizing spin-transistors and -interconnects employing 2D-materials. It is shown that optimized 2D-spin-transistors outperform MOSFETs by yielding more than two-orders of magnitude improvement in energy-efficiency, while Gr spin interconnects can provide diffusion lengths exceeding 25 µm, thereby paving the way for all 2D-spin-logic.

## Session 4: Reliability Of Systems and Devices (RSD) - Protection from ESD, Thermal Runaway and Corrosion

1:30 PM. Continental 1-3

Co-Chairs: Bonnie Weir, Broadcom and Susanna Reggiani, Università di Bologna

The session starts with the analysis of various ESD-protection devices dealing with the most innovative technologies and covers prevention of thermal runaway and corrosion. The first paper from K.U. Leuven, by W-C. Chen, addresses the protection of extremely thin wafers with double-sided connectivity. The next paper, from the University of Illinois, by S. Huang, proposes a novel silicon-controlled rectifier in a finFET technology. The third paper, from NYCU-Taiwan, by Tz-Wun Wang, proposes an ESD-protection methodology for monolithic GaN-on-Silicon. Stephen Poon (TSMC) follows with an invited talk, which gives a general view of ESD reliability in advanced nodes. The fifth talk from Stanford University, by K. Woo, moves on to present innovations in diamond-based cooling to prevent thermal runaway. The final talk from Purdue University, by M. Asaduz Zaman Mamun, presents a holistic approach to prevent wirebond corrosion failure.

### 1:35 PM

### 4-1 ESD Challenges in 300nm Si Substrate of DTCO/STCO Scaling Options

Wen-Chieh Chen<sup>1</sup>, Shih-Hung Chen<sup>2</sup>, Anabela Veloso<sup>2</sup>, Kateryna Serbulova<sup>3</sup>, Geert Hellings<sup>4</sup>, Guido Groeseneken<sup>1</sup>

<sup>1</sup>KULeuven/imec, <sup>2</sup>Imec, <sup>3</sup>KULeuven/Imec, <sup>4</sup>imec

In DTCO/STCO era, sub-µm Si substrate is essential for vertical connections. This work first- time evaluates the ESD performance of various ESD devices with 300nm wafer thickness and nTSV. The thermal dissipation of these ESD devices with BS contact/ metals were studied for a possible solution to the thermal issue.

#### 2:00 PM

### 4-2 Poly-Bounded Silicon-Controlled-Rectifier for ESD Protection in FinFET Technology

Shudong Huang<sup>1</sup>, Srivatsan Parthasarathy<sup>2</sup>, Yuanzhong Zhou<sup>2</sup>, Jean-Jacques Hajjar<sup>2</sup>, Elyse Rosenbaum<sup>1</sup>, University of Illinois at Urbana-Champaign, <sup>2</sup>Analog Devices Inc.

A low-capacitance, low trigger voltage, and fast turn-on silicon-controlled rectifier (SCR) is developed for electrostatic discharge (ESD) protection in a FinFET technology. A deep-Nwell biasing technique is introduced. The proposed SCR device can sink more than 10-A of VFTLP current at 5V and with less than 80-fF of capacitive loading.

#### 2:25 PM

## 4-3 ESD HBM 3kV Discharge for Monolithic GaN-on-Si HEMTs Integrated Chips

Tz-Wun Wang<sup>1</sup>, Chang-Lin Go<sup>1</sup>, Sheng-Hsi Hung<sup>1</sup>, Chi-Yu Chen<sup>1</sup>, Po-Jui Chiu<sup>1</sup>, Ke-Horng Chen<sup>1</sup>, Kuo-Lin Zheng<sup>1,2</sup>, Ying-Hsi Lin<sup>3</sup>, Tsung-Yen Tsai<sup>3</sup>, Shian-Ru Lin<sup>3</sup>,

<sup>1</sup>NYCU, <sup>2</sup>Chip-GaN Power Semiconductor, <sup>3</sup>Realtek Semiconductor

This paper proposes ESD protection in GaN-on-silicon processes. Due to well-designed ESD circuits and tunable geometry of GaN devices, the disadvantage of large  $I_Q$  in conventional ESD schemes can be reduced to 8.11 $\mu$ A, a 222x improvement, by an area-efficient implementation, and discharge 3kV and 100V HBM and MM tests, respectively.

#### 3:15 PM

### 4-4 ESD Reliability in Advanced Nodes (Invited)

Steven Szehang Poon<sup>1</sup>, Ming-Hong Kao<sup>1</sup>, Wei-Chao Chang<sup>1</sup>, T.F. Huang<sup>1</sup>, <sup>1</sup>TSMC

Standard ESD protection structures continue to perform well in advanced technologies. However, Power, Performance, and Area (PPA) considerations have increased the importance of accurately deploying a sufficient but not excessive amount of ESD protection. This invited paper will describe how device and product ESD qualification efforts support these critical changes.

#### 3:40 PM

## 4-5 Interlayer Engineering to Achieve <1 m<sup>2</sup>K/GW Thermal Boundary Resistances to Diamond for Effective Device Cooling

Kelly Woo<sup>1</sup>, Mohamadali Malakoutian<sup>1</sup>, Youhwan Jo<sup>2</sup>, Xiang Zheng<sup>3</sup>, Thomas Pfeifer<sup>4</sup>, Ramandeep Mandia<sup>5</sup>, Taesoon Hwang<sup>2</sup>, Henry Aller<sup>6</sup>, Daniel Field<sup>3</sup>, Patrick Hopkins<sup>4</sup>, Samuel Graham<sup>6</sup>, Martin Kuball<sup>3</sup>, Kyeongjae Cho<sup>2</sup>, Srabanti Chowdhury<sup>1</sup>

<sup>1</sup>Stanford University, <sup>2</sup>UT Dallas, <sup>3</sup>University of Bristol, <sup>4</sup>University of Virginia, <sup>5</sup>Arizona State University, <sup>6</sup>University of Maryland, College Park

Highly localized electric fields and resulting high temperatures can degrade semiconductor devices, leading to premature failure. Diamond with its high thermal conductivity is an effective device/chip level heat-spreader when integrated at the channel/junction. However, a bottleneck lies in the thermal boundary resistance between the hotspot and the heat spreader. Atomistic thermal transport modeling was used to show the reduction of TBR below the diffuse-mismatch theory predictions is possible with a SiC interlayer. Experimentally, the interlayer crystallinity and thickness were engineered to produce TBRs of 3.1±0.7 and 1.89±0.18m²K/GW. This can lead to W-band power to >30 W/mm in GaN HEMTs.

#### 4:05 PM

**4-6** A Holistic Approach to Predict Wirebond Corrosion Failure in Extreme Operating Environments Md Asaduz Zaman Mamun<sup>1</sup>, Amar Mavinkurve<sup>2</sup>, René Rongen<sup>2</sup>, Michiel van Soestbergen<sup>2</sup>, Muhammad A. Alam<sup>1</sup>

<sup>1</sup>Purdue University, <sup>2</sup>NXP Semiconductors

In this study, we: (i) investigate in-situ ion migration behavior in the EMC (under various use conditions) using measured leakage current across the metal-EMC-metal capacitive structure, (ii) determine migrated/ localized ions near the bond pad using 3D numerical simulation, (iii) encapsulate the insights from the simulations and the assumption of a first-order redox reaction into a failure distribution model, and (iv) provide physics-based reasoning for the power-law observed in the empirical accelerated failure model. The proposed model is validated by IC failure data from multiple companies, i.e., Cisco, Motorola, NXP, and Huawei.

## Session 5: Neuromorphic Computing (NC) - Neuromorphic Hardware

1:30 PM, Continental 4

Co-Chairs: Sanghyeon Kim, KAIST and Eric Vogel, Georgia Tech

This session covers bioinspired neuromorphic technologies featuring novel device demonstrations. The first paper describes a dendrite-like device that discriminates spatiotemporal patterns of pulses for parallel processing. The second paper experimentally demonstrated ReRAM devices enabling scalable online e-Prop learning algorithms. The third is an invited paper which describes the fundamental relationship between the switching dynamics of redox-based memristive devices and their analog programming capability for neuromorphic applications. The fourth paper demonstrates that back-end-of-the-line oscillatory neurons based on InGaAs biristors and coupled via capacitive synapses are suitable for solving complex pattern recognition tasks. The final paper demonstrates a multifunction three-dimensional vertical random-access memory array where different layers exhibit nonvolatile properties and volatile characteristics, respectively, can be used to implement multimodal neuromorphic computing tasks such as video recognition.

#### 1:35 PM

**5-1 Multi-gate FeFET Discriminates Spatiotemporal Pulse Sequences for Dendrocentric Learning** Hugo J.-Y. Chen<sup>1</sup>, Matthew Beauchamp<sup>1</sup>, Kasidit Toprasertpong<sup>1</sup>, Fei Huang<sup>1</sup>, Louis Le Coeur<sup>1</sup>, Thorgund Nemec<sup>2</sup>, H.-S. Philip Wong<sup>1</sup>, Kwabena Boahen<sup>1</sup> Stanford University, <sup>2</sup>GlobalFoundries

This paper presents a dendrite-like device that discriminates spatiotemporal patterns of pulses for parallel processing in 3D neuromorphic architectures. The device utilizes the ferroelectric layer in a segmented multigate FeFET design to detect a consecutive sequence of input pulses. Experimental results demonstrate successful emulation of highly selective sequence discrimination in dendrites of neurons in the cortex and highlight up to 100× signal-margin (output current differences). This nanodendrite design offers a neuromorphic solution to thermally scalable parallel processing in 3D systems. 2:00 PM

## 5-2 ReRAM-Based NeoHebbian Synapses for Faster Training-Time-to-Accuracy Neuromorphic Hardware

Tinish Bhattacharya<sup>1</sup>, Sai Sukruth Bezugam<sup>1</sup>, Shubham pande<sup>1,2</sup>, Ewelina Wlazlak<sup>1</sup>, Dmitri Strukov<sup>1</sup>, <sup>1</sup>UC Santa Barbara, <sup>2</sup>IIT Madras

For the first time, NeoHebbian artificial synapses based on ReRAM devices have been proposed and demonstrated, enabling scalable online e-Prop learning. These synapses, with two state variables, use either a pair of ReRAM devices in different configurations or a heater-assisted design for weight updates. Benchmarks show these synapses significantly reduce training time and energy in temporal data modeling applications.

### 2:25 PM

## 5-3 Engineering the kinetics of redox-based memristive devices for neuromorphic computing (Invited)

Regina Dittmann<sup>1</sup>, Alexandros Sarantopoulos<sup>2</sup>, Christopher Bengel<sup>3</sup>, Alexander Gutsche<sup>2</sup>, Felix Cüppers<sup>2</sup>, Susanne Hoffmann-Eifert<sup>2</sup>, Stephan Menzel<sup>2</sup>

<sup>1</sup>Forschungszentrum Jülich, <sup>2</sup>Forschungszentrum Jülich GmbH, <sup>3</sup>RWTH Aachen University

For neuromorphic computing applications, analog programming characteristics with linear updates are highly desirable. Here, we discuss the relation between the switching dynamics of redox-based memristive devices and their analog programming capability. We identify three groups of devices based on the valence change mechanism with characteristic properties. Experimental results and theoretical considerations suggest that analog switching can be achieved if a thermal runaway is avoided. Moreover, we argue that internal series resistances play a crucial role in controlling the runaway and determining the accessible resistance window.

2:50 PM

## 5-4 BEOL-compatible 4F<sup>2</sup> Single Crystalline Semiconductor Oscillator for Low-power and Large-scale Oscillatory Neural Network Hardware

Joon Pyo Kim<sup>1</sup>, Hyun Wook Kim<sup>2</sup>, Jaeyong Jeong<sup>1</sup>, Juhyuk Park<sup>1</sup>, Seong Kwang Kim<sup>1</sup>, Jongmin Kim<sup>3</sup>, Jiyong Woo<sup>2</sup>, Sanghyeon Kim<sup>1</sup>